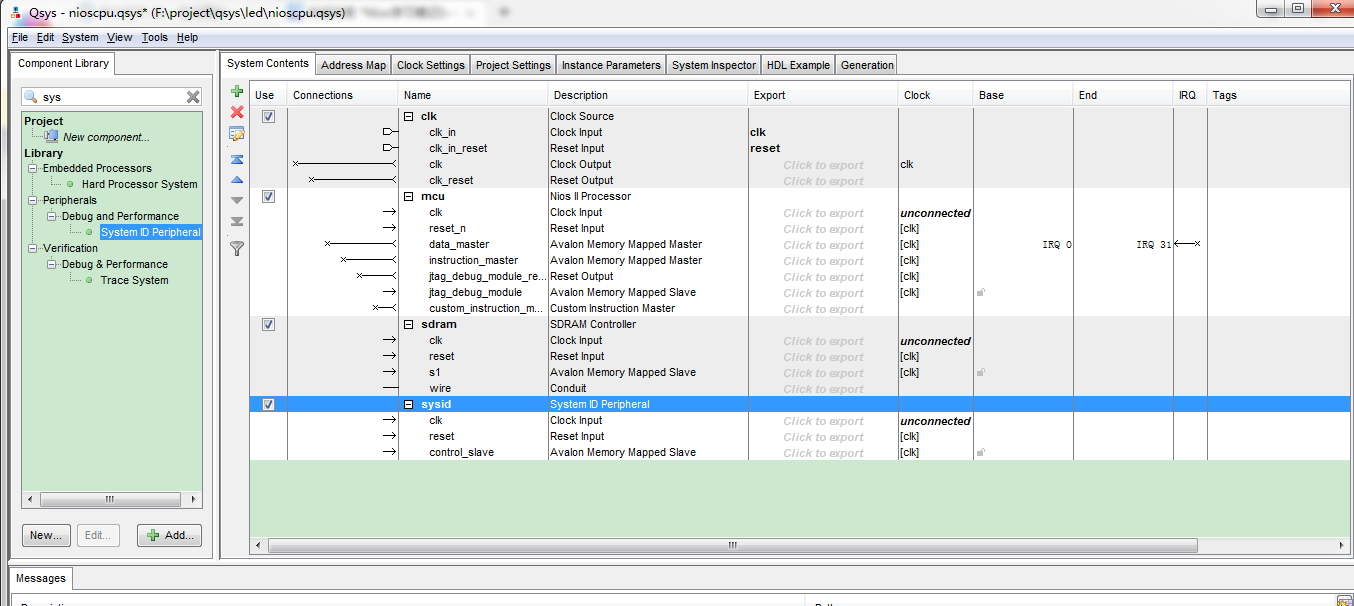

Hi all, I am having problems booting up my Nios C code from EPCS. I am building my own FPGA board, not using a demo board. I'm using Quartus 15.0 and DE0 NanoBoard( Cyclone IV as FPGA) My application contains: 1.

EPCS Serial Flash Controller 6. SDRAM Controller I want to use SDRAM to store instructions and data for NIOS application. In the NIOS II Processor properties reset vector is set to base address of EPCS controller. Exceptions vector is set to base address to SDRAM. In the NIOS EDS for Eclipce I can debug my application, it works. Document Description; Altera MAX10 10M50 Rev C Development Kit Linux Setup (ACDS version 15.1) This page provides information about setting up and running Nios II Linux on Altera MAX10 10M50 Rev C development kit.

Epcs Serial Flash Controller Qsys Driver

Clock Source 2. Nios II Processor 3. EPCS Serial Flash Controller 6. SDRAM Controller I want to use SDRAM to store instructions and data for NIOS application. In the NIOS II Processor properties reset vector is set to base address of EPCS controller. Exceptions vector is set to base address to SDRAM.

Epcs Serial Flash Controller Qsys System

In the NIOS EDS for Eclipce I can debug my application, it works. Hi Frank, Thank you for your answer. I finally success to boot both hardware and software from flash, the problem was i think the clock, because it was configured to be 100 Mhz for the flash controller. When i modified it, to be 25 Mhz, it's ok.

But, now i'm facing another problem. When i try to run the NIOS over JTAG, i can't see any modification. It seems to be kind of jtag communication problem. In the Nios console, i can't see the 'hello word' printed. It worked for me before, it's strange. With the jtagconfig -n command, i get this message (the picture joined) Best regards.